AMD、“Milan”ことZen 3コアに進化した第3世代EPYCを発表 キャッシュ階層の改良でIPCを向上、6chメモリもサポート

AMDは3月15日午前10時(米国東海岸時間、日本時間3月15日午前0時)から、同社CEOのリサ・スー氏による記者会見を開催しており、その中で、同社が開発コード名「Milan」(ミラン、英語でイタリア北部の主要都市「ミラノ」のこと)と呼んできたサーバー向けCPUの最新製品「第3世代AMD EPYCプロセッサー」(AMD EPYC 7003シリーズ、以下は第3世代EPYCと表記)を発表したことを明らかにした。

AMDが発表した第3世代EPYC(出典:AMD)同社のサーバー向けCPUは、2017年に発表された開発コード名「Naples(ネイプルス、英語で南伊の都市ナポリのこと)」ことAMD EPYCプロセッサー(初代EPYC)において、従来製品よりも圧倒的に高効率化されたZen(ゼン)コアを採用し、最大32コアのCPUをリリース。従来は大きな差を付けられていたIntel製品と同等の性能を実現した。

さらに、2019年に発表された開発コード名「Rome(ローマ)」こと第2世代AMD EPYCプロセッサー(以下、第2世代EPYC)では、Zenコアを改良し、IPC(Instruction Per Clock-cycle:1クロックサイクルあたりに実行できる命令数のこと。このIPCが高ければ高いほどCPUは効率よく命令を実行できる)の観点でもIntel製品に追い付いた。

加えて、初代EPYCでも採用していた、複数チップを1つのパッケージに搭載する「チップレット・アーキテクチャ」も第2世代へと進化し、コア数を飛躍的に増やすことが可能になって、1ソケットで64コアを実現。Intelの競合製品を性能で上回ってみせた。

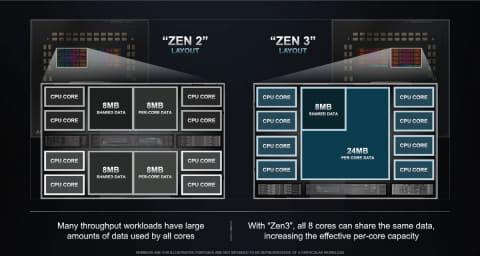

今回の第3世代EPYCでは、CPUのマイクロアーキテクチャが第2世代EPYCのZen 2から新世代のZen 3へと進化しており、キャッシュ階層や内部の分岐予測や実行ユニットなどの見直しなどにより、IPCがさらに高くなっている。

そして、第2世代EPYCではサポート対象外となっていた6チャネルのメモリ構成などにも対応し、より柔軟にメモリ構成を検討することが可能になったという。

また、第2世代EPYCで新たに対応した仮想マシン(VM)向けのセキュリティ機能AMD SEV-ES(Secure Encrypted Virtualization-Encrypted State)が、従来のVMまでのサポートから、ネスト(入れ子にすること)されたVM(VMの中に作られたVM)にも適用になり、VMのセキュリティ性が向上されている。